ANSI/VITA 5.1-1999

Approved as an American National Standard by

# American National Standard for RACEway Interlink

# Secretariat VMEbus International Trade Association

Approved August 31, 1999 American National Standards Institute, Inc.

# American National Standard for RACEway Interlink

# Secretariat **VMEbus International Trade Association**

Approved August 31, 1999 American National Standards Institute, Inc.

# Abstract

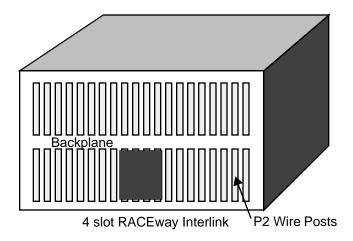

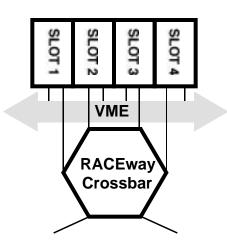

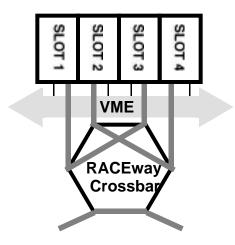

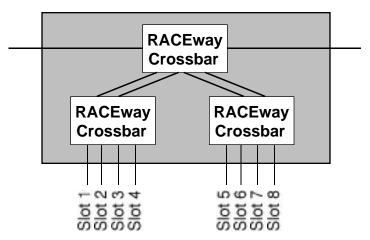

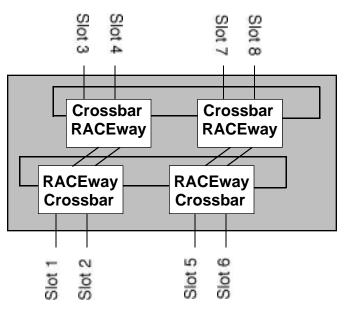

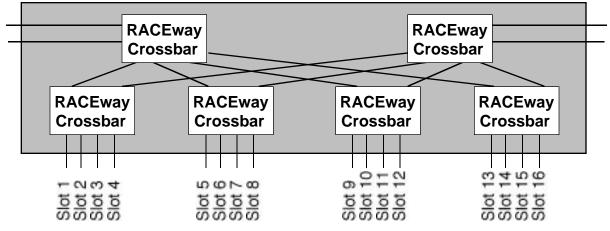

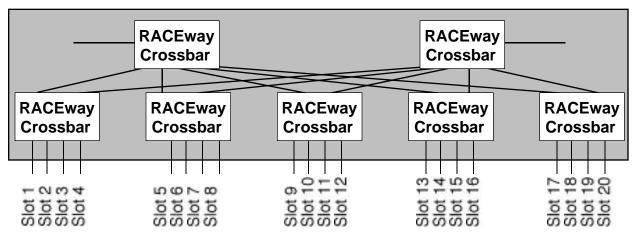

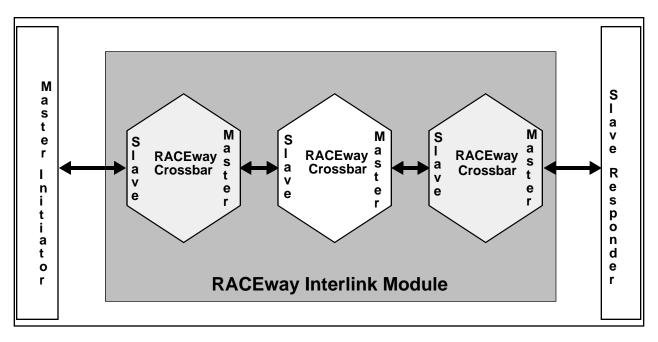

This standard provides a specification of the data link protocol and physical interface of a high performance extension to the VMEbus standard. This extension consists of high bandwidth, low latency interconnects across a VMEbus computer chassis backplane using the P2 connector. Bi-directional connectivity between boards in a VMEbus chassis is achieved through the use of a network of crossbar switches with point-to-point interconnects.

# American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made toward their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether they have approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give an interpretation of any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standard Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

CAUTION NOTICE: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

Published by

# VMEbus International Trade Association 7825 E. Gelding Drive, Suite 104, Scottsdale, AZ 85260

Copyright © 1999 by VITA, the VMEbus International Trade Association All rights reserved.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without prior written permission of the publisher.

Printed in the United States of America

ISBN 1-885731-22-1

# **Table of Contents**

| Lis<br>Lis | ble of Contentsi<br>t of Tablesi<br>t of Figuresv<br>rewordv | v<br>v |

|------------|--------------------------------------------------------------|--------|

| Inti       | roduction                                                    | 1      |

| 1          | Scope and purpose                                            | 5      |

| 1.1        | Scope                                                        | .5     |

| 1.2        | Purpose                                                      | .5     |

| 1.3        | Normative references                                         | .5     |

| 2          | Definitions                                                  | 7      |

| 2.1        | Key words                                                    | .7     |

| 2.2        | General                                                      | .7     |

| 2.3        | Protocol                                                     | .7     |

| 2.4        | Physical                                                     | .9     |

| 3          | Overview 1                                                   | 1      |

| 3.1        | Characteristics1                                             | 1      |

| 3          | 3.1.1 VMEbus compatibility 1                                 | 1      |

| 3          | 3.1.2 Interconnectivity 1                                    | 1      |

| 3          | 3.1.3 Transaction size 1                                     | 1      |

| 3          | 3.1.4 Resource Contention 1                                  | 1      |

| 3          | 3.1.5 Physical 1                                             | 1      |

| 3.2        | Fundamental concepts1                                        | 1      |

| 3          | 3.2.1 Crossbar network 1                                     | 1      |

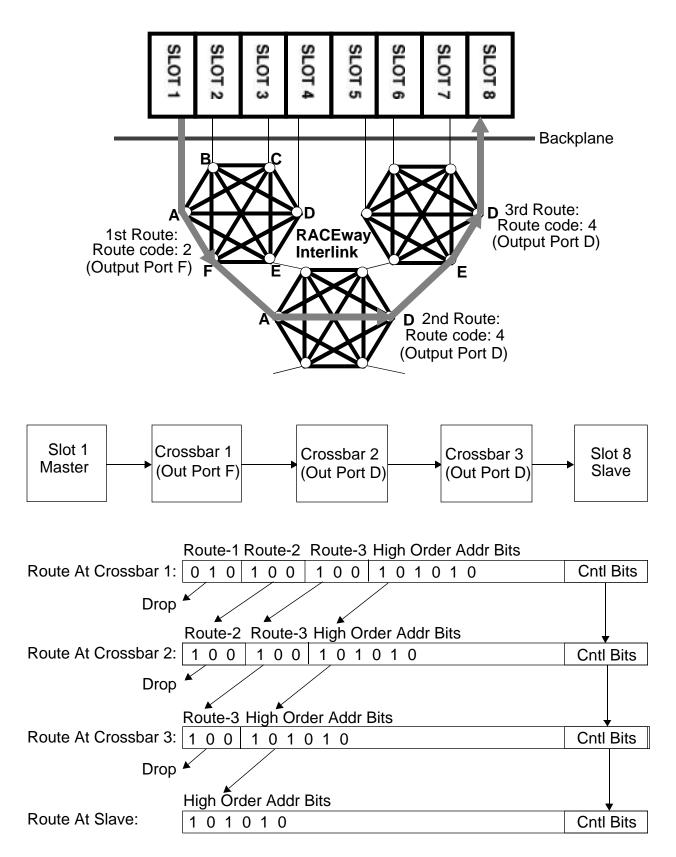

| 3          | 3.2.2 Routing 1                                              | 1      |

| 3          | 3.2.3 Handshaking 1                                          | 3      |

| 3          | 3.2.4 Configuration 1                                        | 4      |

| 3          | 3.2.5 Latency 1                                              | 4      |

| 3          | 3.2.6 Priorities and Kill requests 1                         | 4      |

| 3          | 3.2.7 Adaptive routing 1                                     | 4      |

| 3          | 3.2.8 Locked operations 1                                    | 4      |

| 3          | 3.2.9 Split read transfers 1                                 | 4      |

| 3          | 3.2.10 Split write transfers1                                | 5      |

| 4.1       Transaction format       17         4.2       Extended route/address format       18         4.3       Routing code/Broadcast Mode       19         4.4       Broadcast acceptance code       20         4.5       Routing priority code       21         4.6       Transfer width and alignment specification       23         4.7       Address       24         4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO                                                                       | 4                                                                                                           | A Data Link Layer specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3       Routing code/Broadcast Mode       19         4.4       Broadcast acceptance code       20         4.5       Routing priority code       21         4.6       Transfer width and alignment specification       23         4.7       Address       24         4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4                                                                   | 4.1                                                                                                         | Transaction format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                                                                                                                                                                                             |

| 4.4       Broadcast acceptance code       20         4.5       Routing priority code       21         4.6       Transfer width and alignment specification       23         4.7       Address       24         4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases.       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.       35         5.9.3       Address phase: CHANGE TO ADDRESS.       35         5.9.4       Data phase: ASTROBE and DSTROBE.       39                                                                | 4.2                                                                                                         | Extended route/address format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18                                                                                                                                                                                             |

| 4.5       Routing priority code       21         4.6       Transfer width and alignment specification       23         4.7       Address       24         4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: CHANGE TO ADDRESS       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6 <t< td=""><td>4.3</td><td>Routing code/Broadcast Mode</td><td>19</td></t<> | 4.3                                                                                                         | Routing code/Broadcast Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                                                                                                             |

| 4.6       Transfer width and alignment specification       23         4.7       Address       24         4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: CHANGE TO ADDRESS       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7                                                                              | 4.4                                                                                                         | Broadcast acceptance code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                                                                                                             |

| 4.7       Address       24         4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       <                                                                   | 4.5                                                                                                         | Routing priority code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                                                                                                                                             |

| 4.8       Reserved field       24         4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44                                            | 4.6                                                                                                         | Transfer width and alignment specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                                                                                                                                                             |

| 4.9       Reads       25         4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transactions       43         5.9.9       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44         5.9.9       Data phase during Reads: RDCON* and ERR       45         5.9.10       Read transaction       47                           | 4.7                                                                                                         | Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                             |

| 4.10       Locked transfers       25         5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44         5.9.9       Data phase during Reads: RDCON* and ERR       45         5.9.10       Read trans                  | 4.8                                                                                                         | Reserved field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                                                                                                                                                             |

| 5       Physical layer specification       27         5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44         5.9.9       Data phase during Reads: RDCON* and ERR       45         5.9.10       Read transaction       47         5.9.11       Read-Mod                  | 4.9                                                                                                         | Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                                                                                                                                             |

| 5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44         5.9.9       Data phase during Reads: RDCON* and ERR       45         5.9.10       Read transaction       47         5.9.12       Read-Modify-Write transaction       48         5.9.13       Re                  | 4.10                                                                                                        | Locked transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                                                                                                                             |

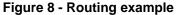

| 5.1       Interface       27         5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44         5.9.9       Data phase during Reads: RDCON* and ERR       45         5.9.10       Read transaction       47         5.9.12       Read-Modify-Write transaction       48         5.9.13       Re                  | 5                                                                                                           | Physical layer specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                                                                                                                                                             |

| 5.2       Connections       27         5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44       5.9.10         5.9.10       Read transaction       46         5.9.10       Read transaction       47         5.9.12       Read-Modify-Write transaction       48         5.9.13       Read-Modify-Write transaction       49                            |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 5.3       P2 Pinout       28         5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases.       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.       35         5.9.3       Address phase: CHANGE TO ADDRESS.       35         5.9.4       Data phase: DSEN.       37         5.9.5       Data phase: ASTROBE and DSTROBE.       39         5.9.6       Write transaction.       41         5.9.7       Broadcast write transactions.       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44       5.9.9         5.9.10       Read transaction.       47         5.9.11       Read transaction.       47         5.9.12       Read-Modify-Write transaction       48         5.9.13       Read-Modify-Write transaction       49                                                           | -                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 5.4       Master interface signals to the RACEway crossbar network       29         5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE       35         5.9.3       Address phase: CHANGE TO ADDRESS       35         5.9.4       Data phase: DSEN       37         5.9.5       Data phase: ASTROBE and DSTROBE       39         5.9.6       Write transaction       41         5.9.7       Broadcast write transactions       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44       5.9.10 Read transaction       46         5.9.10       Read transaction       47       47       5.9.12       Read-Modify-Write transaction       48         5.9.13       Read-Modify-Write transaction       49       49                                                                                                             | -                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 5.5       Slave interface signals to the RACEway crossbar network       30         5.6       Signal characteristics       31         5.7       Signal notation       31         5.8       Master/slave relationship       32         5.9       Timing       33         5.9.1       Clocks and control phases.       33         5.9.2       Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.       35         5.9.3       Address phase: CHANGE TO ADDRESS.       35         5.9.4       Data phase: DSEN.       37         5.9.5       Data phase: ASTROBE and DSTROBE.       39         5.9.6       Write transaction.       41         5.9.7       Broadcast write transactions.       43         5.9.8       Data phase during Reads: ASTROBE, DSTROBE and READ READY 44       5.9.9         5.9.10       Read transaction.       46         5.9.11       Read transaction.       47         5.9.12       Read-Modify-Write transaction       48         5.9.13       Read-Modify-Write transaction       49                                                                                                                                                                                    |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 5.6Signal characteristics315.7Signal notation315.8Master/slave relationship325.9Timing335.9.1Clocks and control phases335.9.2Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE355.9.3Address phase: CHANGE TO ADDRESS355.9.4Data phase: DSEN375.9.5Data phase: ASTROBE and DSTROBE395.9.6Write transaction415.9.7Broadcast write transactions435.9.8Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9Data phase during Reads: RDCON* and ERR455.9.10Read transaction475.9.12Read-Modify-Write transaction485.9.13Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 5.7Signal notation315.8Master/slave relationship325.9Timing335.9.1Clocks and control phases335.9.2Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE355.9.3Address phase: CHANGE TO ADDRESS355.9.4Data phase: DSEN375.9.5Data phase: ASTROBE and DSTROBE395.9.6Write transaction415.9.7Broadcast write transactions435.9.8Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9Data phase during Reads: RDCON* and ERR455.9.10Read transaction465.9.11Read transaction475.9.12Read-Modify-Write transaction485.9.13Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                |

| 5.8Master/slave relationship325.9Timing335.9.1Clocks and control phases.335.9.2Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.355.9.3Address phase: CHANGE TO ADDRESS.355.9.4Data phase: DSEN.375.9.5Data phase: ASTROBE and DSTROBE.395.9.6Write transaction.415.9.7Broadcast write transactions.435.9.8Data phase during Reads: ASTROBE, DSTROBE and READ READY 44445.9.9Data phase during Reads: RDCON* and ERR.455.9.10Read transaction.475.9.12Read-Modify-Write transaction485.9.13Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                                                                                          | Signal characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                                                                                                             |

| 5.9Timing335.9.1Clocks and control phases.335.9.2Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.355.9.3Address phase: CHANGE TO ADDRESS.355.9.4Data phase: DSEN.375.9.5Data phase: ASTROBE and DSTROBE.395.9.6Write transaction.415.9.7Broadcast write transactions.435.9.8Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9Data phase during Reads: RDCON* and ERR.455.9.10Read transaction.475.9.12Read-Modify-Write transaction485.9.13Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                |

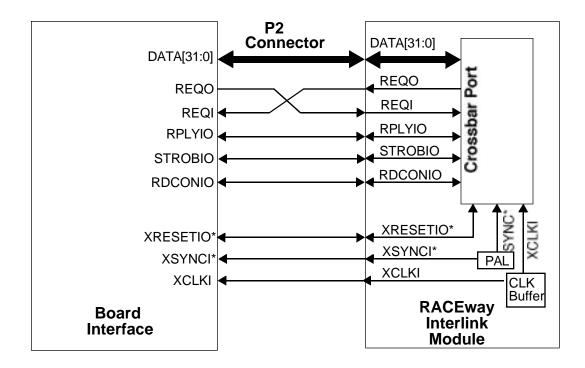

| 5.9.1 Clocks and control phases.335.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.355.9.3 Address phase: CHANGE TO ADDRESS.355.9.4 Data phase: DSEN.375.9.5 Data phase: ASTROBE and DSTROBE.395.9.6 Write transaction.415.9.7 Broadcast write transactions.435.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9 Data phase during Reads: RDCON* and ERR.455.9.10 Read transaction.475.9.12 Read-Modify-Write transaction485.9.13 Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.7                                                                                                         | Signal notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                                                                                                                                                             |

| 5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.7<br>5.8                                                                                                  | Signal notation<br>Master/slave relationship                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>32                                                                                                                                                                                       |

| 5.9.3 Address phase: CHANGE TO ADDRESS.355.9.4 Data phase: DSEN.375.9.5 Data phase: ASTROBE and DSTROBE.395.9.6 Write transaction.415.9.7 Broadcast write transactions.435.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9 Data phase during Reads: RDCON* and ERR.455.9.10 Read transaction.465.9.11 Read transaction.475.9.12 Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.7<br>5.8<br>5.9                                                                                           | Signal notation<br>Master/slave relationship<br>Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31<br>32<br>33                                                                                                                                                                                 |

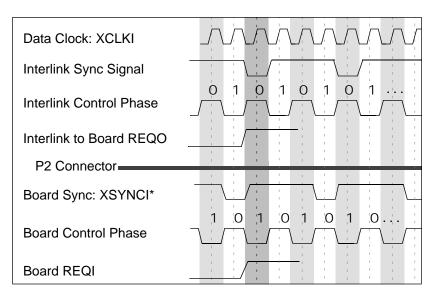

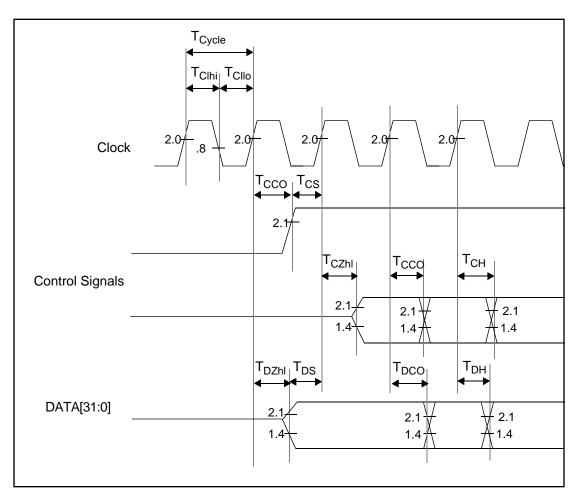

| 5.9.4 Data phase: DSEN.375.9.5 Data phase: ASTROBE and DSTROBE.395.9.6 Write transaction.415.9.7 Broadcast write transactions.435.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9 Data phase during Reads: RDCON* and ERR.455.9.10 Read transaction.465.9.11 Read transaction.475.9.12 Read-Modify-Write transaction485.9.13 Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.7<br>5.8<br>5.9                                                                                           | Signal notation<br>Master/slave relationship<br>Timing<br>5.9.1 Clocks and control phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>31</b><br><b>32</b><br><b>33</b><br>33                                                                                                                                                      |

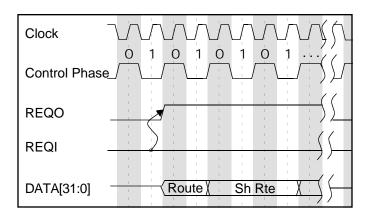

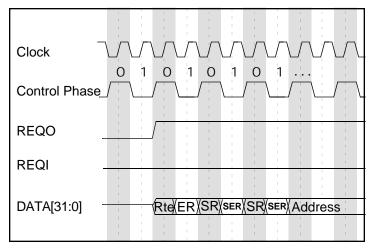

| 5.9.5 Data phase: ASTROBE and DSTROBE.395.9.6 Write transaction.415.9.7 Broadcast write transactions.435.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9 Data phase during Reads: RDCON* and ERR.455.9.10 Read transaction.465.9.11 Read transaction.475.9.12 Read-Modify-Write transaction485.9.13 Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.7<br>5.8<br>5.9                                                                                           | Signal notation<br>Master/slave relationship<br>Timing<br>5.9.1 Clocks and control phases<br>5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> </ul>                                                                                                                                     |

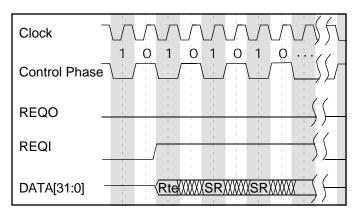

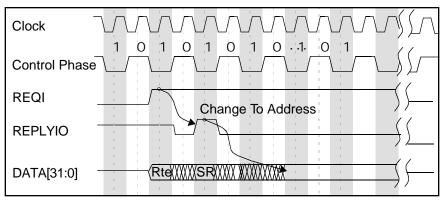

| 5.9.6 Write transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.7<br>5.8<br>5.9<br>5<br>5                                                                                 | Signal notation<br>Master/slave relationship                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> </ul>                                                                                                                         |

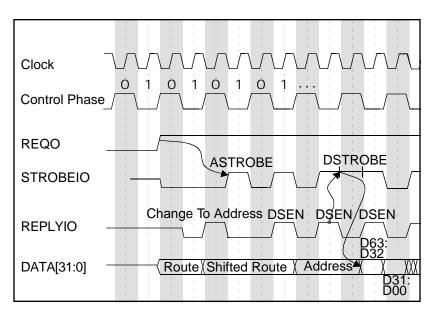

| 5.9.7 Broadcast write transactions.435.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9 Data phase during Reads: RDCON* and ERR.455.9.10 Read transaction.465.9.11 Read transaction.475.9.12 Read-Modify-Write transaction485.9.13 Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5                                                                       | Signal notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> </ul>                                                                                                             |

| 5.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READY 445.9.9 Data phase during Reads: RDCON* and ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5<br>5                                                                  | Signal notation<br>Master/slave relationship<br>Timing<br>5.9.1 Clocks and control phases<br>5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE<br>5.9.3 Address phase: CHANGE TO ADDRESS<br>5.9.4 Data phase: DSEN<br>5.9.5 Data phase: ASTROBE and DSTROBE                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> </ul>                                                                                                 |

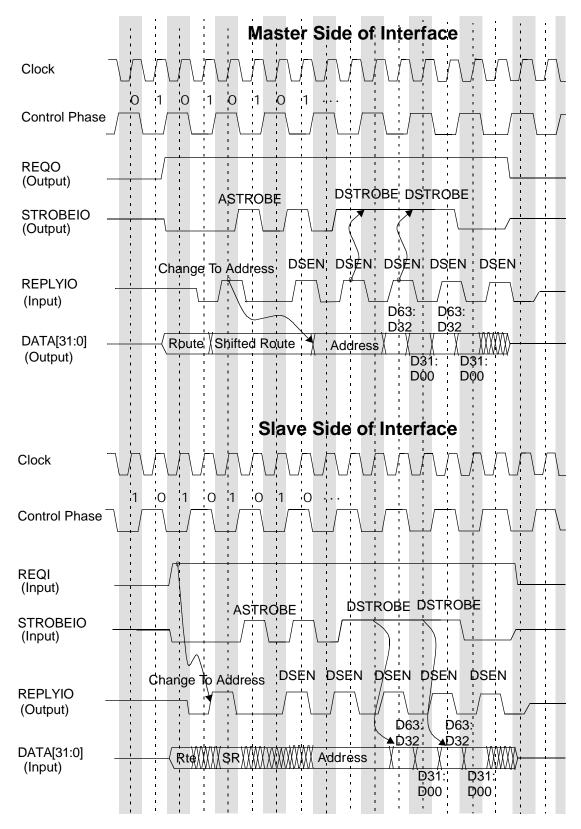

| 5.9.9 Data phase during Reads: RDCON* and ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>5.7</b><br><b>5.8</b><br><b>5.9</b><br>5<br>5<br>5<br>5<br>5                                             | Signal notation         Master/slave relationship         Timing         5.9.1 Clocks and control phases.         5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.         5.9.3 Address phase: CHANGE TO ADDRESS.         5.9.4 Data phase: DSEN.         5.9.5 Data phase: ASTROBE and DSTROBE.         5.9.6 Write transaction.                                                                                                                                                                                                                                                                               | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> </ul>                                                                                     |

| 5.9.10 Read transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5                                              | Signal notation         Master/slave relationship         Timing         5.9.1 Clocks and control phases.         5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.         5.9.3 Address phase: CHANGE TO ADDRESS.         5.9.4 Data phase: DSEN.         5.9.5 Data phase: ASTROBE and DSTROBE.         5.9.6 Write transaction.         5.9.7 Broadcast write transactions.                                                                                                                                                                                                                                   | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>43</li> </ul>                                                                         |

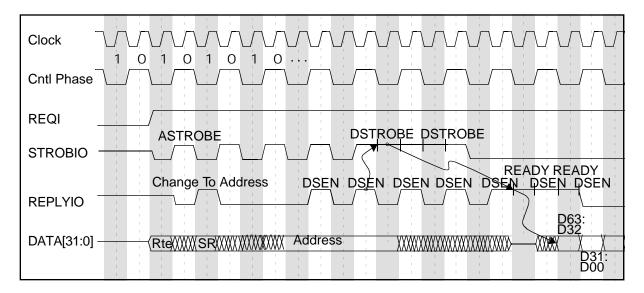

| 5.9.11 Read transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5                                                   | Signal notation         Master/slave relationship         Timing         5.9.1 Clocks and control phases.         5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.         5.9.3 Address phase: CHANGE TO ADDRESS.         5.9.4 Data phase: DSEN.         5.9.5 Data phase: ASTROBE and DSTROBE.         5.9.6 Write transaction.         5.9.7 Broadcast write transactions.         5.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READ                                                                                                                                                             | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>43</li> <li>( 44</li> </ul>                                                           |

| 5.9.12 Read-Modify-Write transaction485.9.13 Read-Modify-Write transaction49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5                                         | Signal notation         Master/slave relationship         Timing         5.9.1 Clocks and control phases.         5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.         5.9.3 Address phase: CHANGE TO ADDRESS.         5.9.4 Data phase: DSEN.         5.9.5 Data phase: ASTROBE and DSTROBE.         5.9.6 Write transaction.         5.9.7 Broadcast write transactions.         5.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READ         5.9.9 Data phase during Reads: RDCON* and ERR.                                                                                                      | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>43</li> <li>( 44</li> <li>45</li> </ul>                                               |

| 5.9.13 Read-Modify-Write transaction 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5                                    | Signal notation         Master/slave relationship         Timing         5.9.1 Clocks and control phases.         5.9.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE.         5.9.3 Address phase: CHANGE TO ADDRESS.         5.9.4 Data phase: DSEN.         5.9.5 Data phase: ASTROBE and DSTROBE.         5.9.6 Write transaction.         5.9.7 Broadcast write transactions.         5.9.8 Data phase during Reads: ASTROBE, DSTROBE and READ READ         5.9.9 Data phase during Reads: RDCON* and ERR.         5.9.10 Read transaction.                                                                     | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>43</li> <li>44</li> <li>45</li> <li>46</li> </ul>                                     |

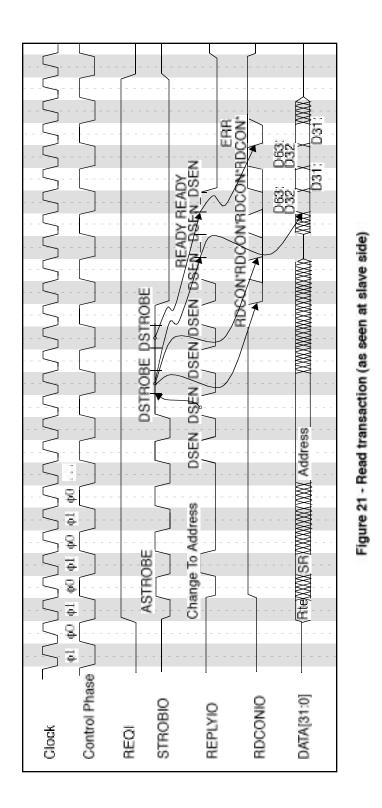

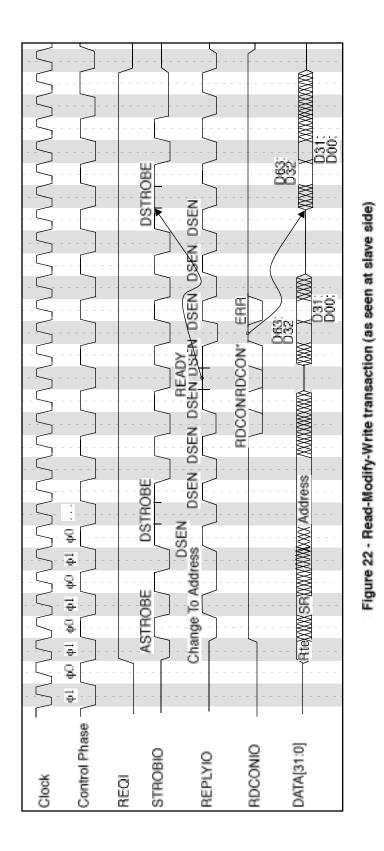

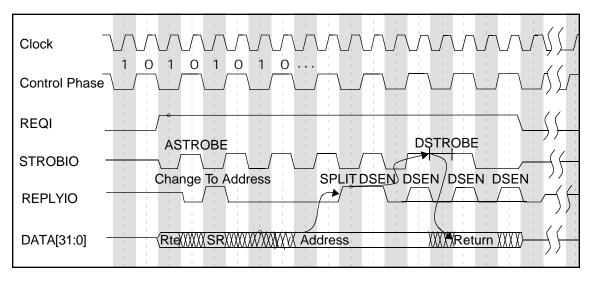

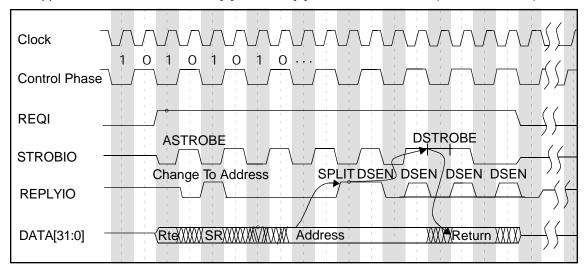

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.7<br>5.8<br>5.9<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5      | Signal notation         Master/slave relationship         Timing         59.1 Clocks and control phases         59.2 Route phase: REQO, REQI, ROUTE, SHIFTED ROUTE         59.3 Address phase: CHANGE TO ADDRESS         59.4 Data phase: DSEN         59.5 Data phase: ASTROBE and DSTROBE         59.6 Write transaction         59.7 Broadcast write transactions         59.8 Data phase during Reads: ASTROBE, DSTROBE and READ READ         59.9 Data phase during Reads: RDCON* and ERR         59.10 Read transaction         59.11 Read transaction                                                         | <ul> <li>31</li> <li>32</li> <li>33</li> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>43</li> <li>(44</li> <li>45</li> <li>46</li> <li>47</li> </ul>                        |